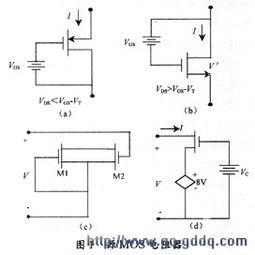

在前兩篇探討了MOSFET的基本結(jié)構(gòu)與工作原理后,我們進入核心應(yīng)用階段——將數(shù)以億計的MOS器件高效、可靠地集成到單一芯片上,即超大規(guī)模集成電路(VLSI)設(shè)計。此過程絕非簡單堆砌,而是涉及從物理原理到系統(tǒng)架構(gòu)的多層次、跨學(xué)科協(xié)同。本文將聚焦于集成電路設(shè)計環(huán)節(jié),闡述如何基于MOS器件原理進行實際電路與系統(tǒng)的構(gòu)建。

一、 從器件到電路:基本單元設(shè)計

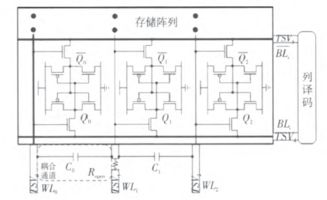

集成電路設(shè)計始于基本功能單元,如反相器(Inverter)、與非門(NAND)、或非門(NOR)以及各類觸發(fā)器(Flip-Flop)。這些單元的性能直接取決于其內(nèi)部MOS器件的特性。

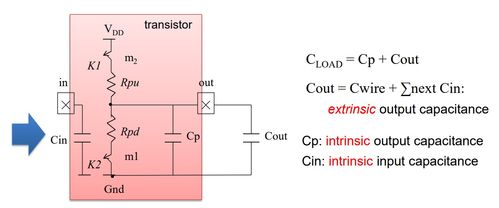

- 靜態(tài)特性與噪聲容限:通過合理設(shè)計PMOS與NMOS的尺寸比例(β比例),可以優(yōu)化反相器的電壓傳輸特性(VTC),確保其具有足夠的噪聲容限(Noise Margin),以抵抗芯片內(nèi)部信號串?dāng)_和電源噪聲帶來的干擾。

- 動態(tài)特性與速度:電路單元的開關(guān)速度(延遲時間)主要由對負(fù)載電容的充放電速度決定。這要求設(shè)計者根據(jù)MOS器件的跨導(dǎo)(gm)和溝道電阻,精心計算驅(qū)動管的尺寸,以在速度與功耗、面積之間取得平衡。晶體管的開關(guān)特性(如上升/下降時間)直接影響時鐘頻率和系統(tǒng)性能。

二、 設(shè)計約束的權(quán)衡:性能、功耗與面積(PPA)

在VLSI設(shè)計中,性能(速度)、功耗和芯片面積構(gòu)成了永恒的“鐵三角”約束,三者往往相互制約。

- 性能與功耗的矛盾:為了提高電路速度(如提升時鐘頻率),通常需要增大晶體管尺寸以提供更大驅(qū)動電流,但這會直接導(dǎo)致動態(tài)功耗(CV2f)和靜態(tài)泄漏功耗的增加。先進工藝節(jié)點下,泄漏功耗的管理尤為關(guān)鍵。

- 面積與成本的考量:更小的晶體管尺寸有助于提高集成密度、降低成本,但會帶來顯著的短溝道效應(yīng),如閾值電壓下降、漏電流增大等,對器件可靠性和電路穩(wěn)定性構(gòu)成挑戰(zhàn)。設(shè)計時必須進行精密的版圖規(guī)劃(Floorplanning)和布局布線(Place & Route),以最小化互連延遲和面積。

三、 互連線的挑戰(zhàn)

在納米級工藝中,金屬互連線產(chǎn)生的電阻(R)和電容(C)效應(yīng)已變得與晶體管性能同等重要,甚至成為主導(dǎo)。

- RC延遲:信號在長互連線上傳播的延遲可能超過邏輯門本身的延遲。這要求設(shè)計階段采用插入緩沖器、優(yōu)化布線拓?fù)洹⑹褂玫蚹介質(zhì)材料等策略來減少信號傳輸時間。

- 串?dāng)_與可靠性:密集的布線間會產(chǎn)生耦合電容,導(dǎo)致信號串?dāng)_(Crosstalk),可能引發(fā)邏輯錯誤。電流密度過大會引發(fā)電遷移(Electromigration)問題,影響芯片長期可靠性。這些都需要在物理設(shè)計階段通過設(shè)計規(guī)則檢查(DRC)和電氣規(guī)則檢查(ERC)進行嚴(yán)格規(guī)避。

四、 設(shè)計方法學(xué)與流程

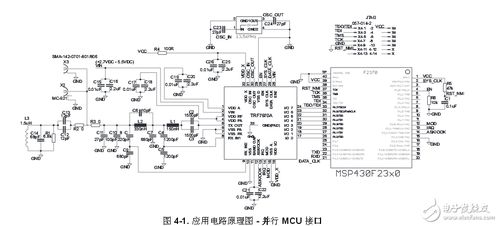

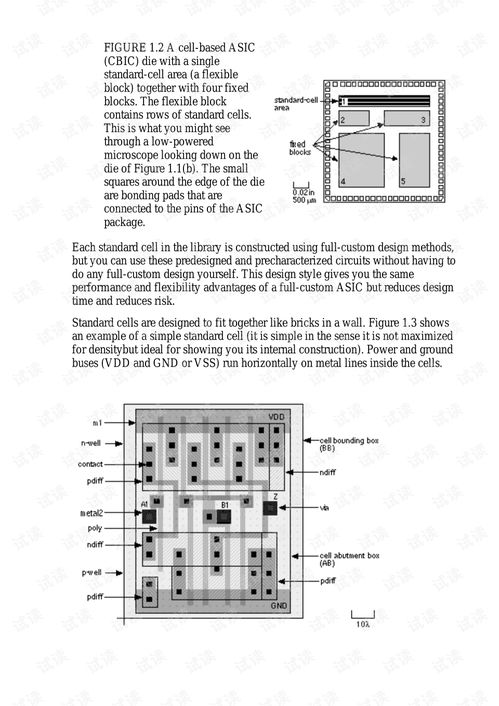

現(xiàn)代VLSI設(shè)計依賴于高度自動化的電子設(shè)計自動化(EDA)工具和分層式設(shè)計方法。

- 自頂向下設(shè)計:從系統(tǒng)級規(guī)范開始,逐步細(xì)化為寄存器傳輸級(RTL)描述、邏輯綜合、物理實現(xiàn)等。每一層都基于對下層MOS器件行為的抽象模型(如SPICE模型、標(biāo)準(zhǔn)單元庫)。

- 仿真與驗證:在流片(Tape-out)前,必須進行全面的仿真驗證,包括前端的功能仿真、時序分析,以及后端的寄生參數(shù)提取(PEX)和版圖后仿真(Post-layout Simulation),以確保電路在實際的器件特性和寄生效應(yīng)下仍能正常工作。

五、 先進技術(shù)的影響

隨著工藝進入深亞微米及以下,新的器件結(jié)構(gòu)(如FinFET、GAA)和設(shè)計技術(shù)協(xié)同優(yōu)化(DTCO)變得至關(guān)重要。這些技術(shù)旨在更好地控制溝道、降低功耗、提升性能,但同時也給電路設(shè)計帶來了新的模型、規(guī)則和挑戰(zhàn)。

****

MOS器件原理是超大規(guī)模集成電路設(shè)計的基石。從微觀的載流子輸運,到宏觀的GHz級處理器,連接兩者的是一座由嚴(yán)謹(jǐn)設(shè)計方法、精妙權(quán)衡藝術(shù)和先進制造工藝構(gòu)筑的橋梁。理解并駕馭MOS器件在集成環(huán)境下的復(fù)雜行為,是設(shè)計出高性能、低功耗、高可靠芯片的關(guān)鍵。隨著集成電路不斷向更小尺度、更高復(fù)雜度邁進,這種基于物理原理的工程設(shè)計思維將愈發(fā)重要。